Un equipo de investigadores del Grupo de Ingeniería Electrónica (GEE) del Instituto de Inteligencia Artificial de las Islas Baleares (IAIB), centro propio de la Universidad de las Islas Baleares (UIB), ha logrado un avance en el campo del procesamiento inteligente de altas prestaciones. En este sentido, han diseñado y fabricado un chip que implementa una arquitectura innovadora para la inteligencia artificial (IA), pensada para entornos en los que el consumo energético es crítico, como dispositivos IoT (internet de las cosas) y sistemas de computación en la frontera (edge computing).

El diseño se basa en redes neuronales morfológicas para reducir el consumo y mantener la precisión en entornos con recursos limitados. La fabricación del chip ha contado con el apoyo del programa Innova UIB-PIMES, en el marco del Espai Valida, orientado a la maduración de proyectos de I+D mediante pruebas de concepto. Esta iniciativa identifica resultados científicos con potencial para transformarse en productos, servicios o ideas de negocio innovadoras e impulsa su transferencia al mercado dentro de la comunidad universitaria.

IA eficiente y computación estocástica

El chip se basa en el uso de computación estocástica para implementar una red neuronal morfológica altamente paralela. Esta estrategia permite un notable incremento de la eficiencia energética, ya que la computación estocástica requiere órdenes de magnitud menos recursos de hardware que la computación digital clásica.

La naturaleza probabilística de esta computación implica que las operaciones básicas tienen una precisión limitada. Sin embargo, cuando se encadenan cientos de miles de operaciones para tareas como el reconocimiento de imágenes o sonidos, la precisión global apenas se degrada: las desviaciones intermedias tienden a cancelarse. Esta misma característica probabilística incrementa la robustez del circuito y permite reducir la tensión de alimentación del chip por debajo de los márgenes habituales de los circuitos digitales convencionales.

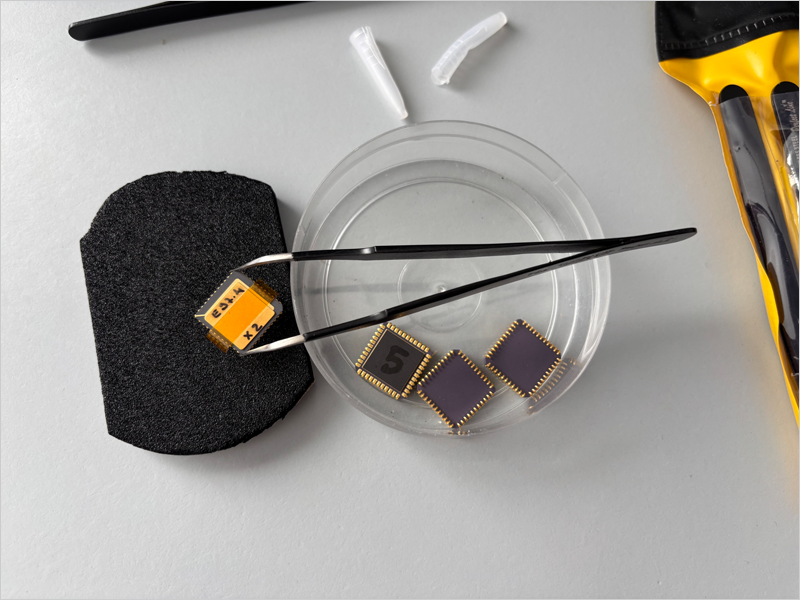

Chip CMOS de bajo consumo para dispositivos IoT

El prototipo se ha fabricado en tecnología CMOS de 180 nm y opera con una tensión de 0,81 voltios. Las pruebas con la base de datos MNIST, que incluye 70.000 imágenes de dígitos manuscritos del 0 al 9, muestran que el chip alcanza una eficiencia energética superior a 1 TOPS/W (un billón de operaciones por julio) con consumos inferiores a 1 mW. Según el equipo, estas cifras mejoran en muchos casos las de arquitecturas alternativas fabricadas con tecnologías CMOS más avanzadas.

Los investigadores señalan que la arquitectura de IA eficiente se considera especialmente adecuada para sensores inteligentes, wearables y sistemas de monitorización distribuidos, donde no es viable disponer de grandes sistemas de cálculo.